Project Category: Electrical

Join our presentation

About our project

Acceleware, a leading innovator in the Oil and Gas Field have been pursuing a method of clean oil extraction using a high powered radio frequency (RF) signal generator. Our group has been provided an opportunity to work on with their development cycle by designing a Field-Programmable Gate Array (FPGA) based prototype controller for operating this high power signal generator for Oil Sands extraction.

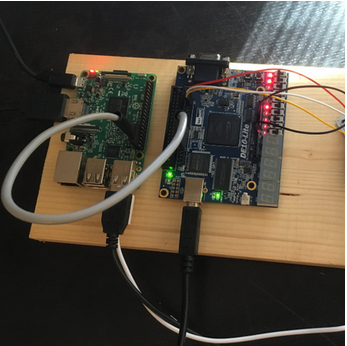

The design consists of two hardware components alongside an interactive web-server that analyze and control a high power generator. The web-server provides a extensible platform for users to control parameters and analyze incoming data from the generator in real time. The pipeline that allows our web-server to receive/send generator information in is through our high frequency DE10-Lite FPGA board which then is processed and stored by the Raspberry Pi to be user friendly. The software foundation of both hardware components were built with extensibility in mind to allow for future hardware alterations.

Our final product will offer Acceleware an on hand prototype for algorithm development and optimization in antenna/generator implementation.

Meet our team members

Asadullah Aftab

hARDWARE lEAD

Alexander Le

Test and user interface lead

Yiyong (Andy) Zheng

Project Manager

John Carlo Catapang

FPGA lead

Taha Ghazaly

Software And Technical lead

Details about our design

HOW OUR DESIGN ADDRESSES PRACTICAL ISSUES

Currently, Acceleware have a controller design which uses a Dspace Field Programmable Gate Array Board with a remote desk that is expensive to maintain and provides the company with a software that has a steep learning curve. The design Acceleware had built was a piece of lab gear which required a full professional license to run and was deemed overkill in performance. Fortunately, the operating conditions of the generator changed slowly so not much signal processing was required to keep up, thus downsizing their design was ideal.

The design we have created provides Acceleware a solution which resolves the main pain points highlighted. With performance, our design provides adequate control and signal processing for their generator in real time. With time, our design provides well documented python and VHDL code that is extensible and easy to comprehend. With pricing, total hardware design was in the ballpark of ~500$ while all software written used open source libraries and was done on free platforms.

WHAT MAKES OUR DESIGN INNOVATIVE

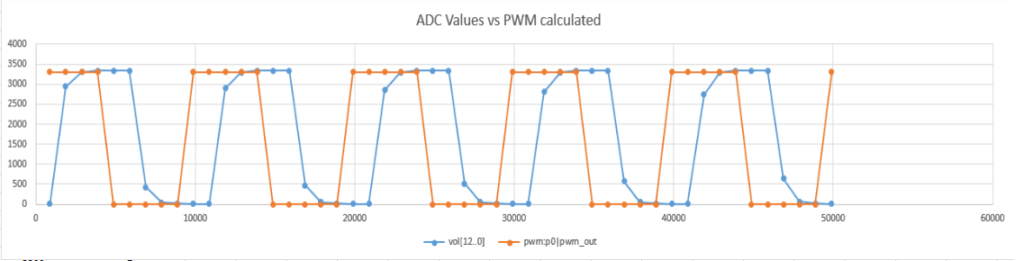

While our project does not make any groundbreaking advancements in FPGA and Raspberry Pi hardware design, we were required to reformat portions of our FPGA board as the manufacturer’s specifications did not match our design requirements. This allowed us to provide clean data samples from our generator which greatly improved our web server results.

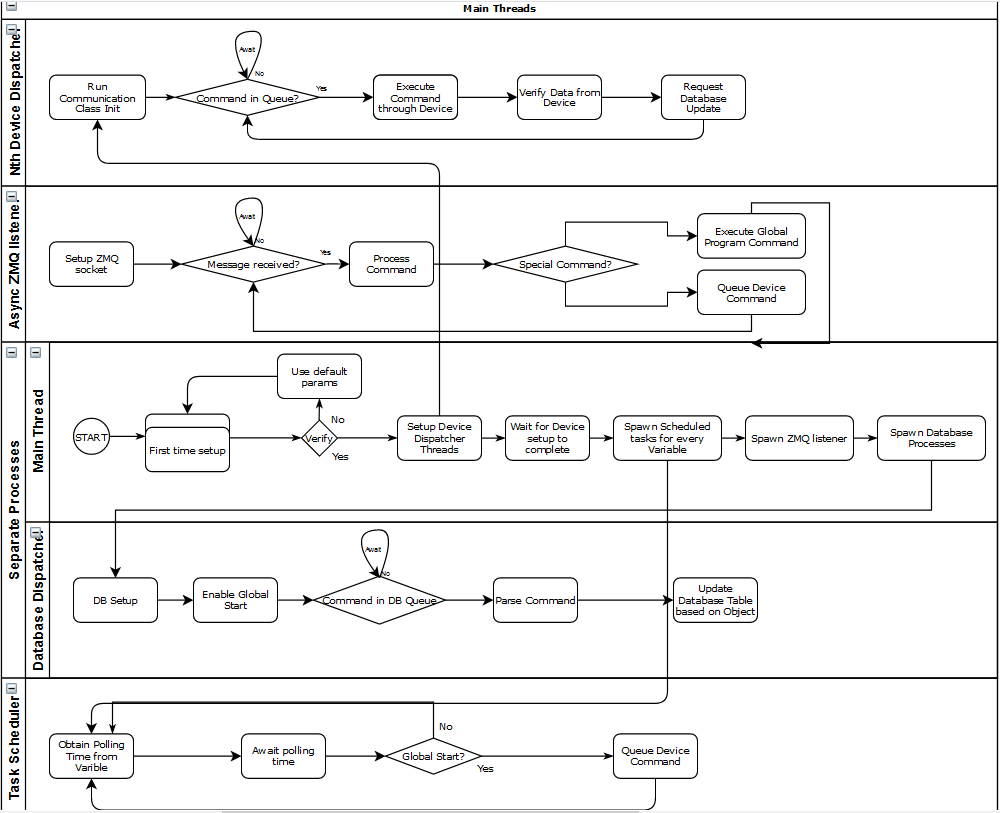

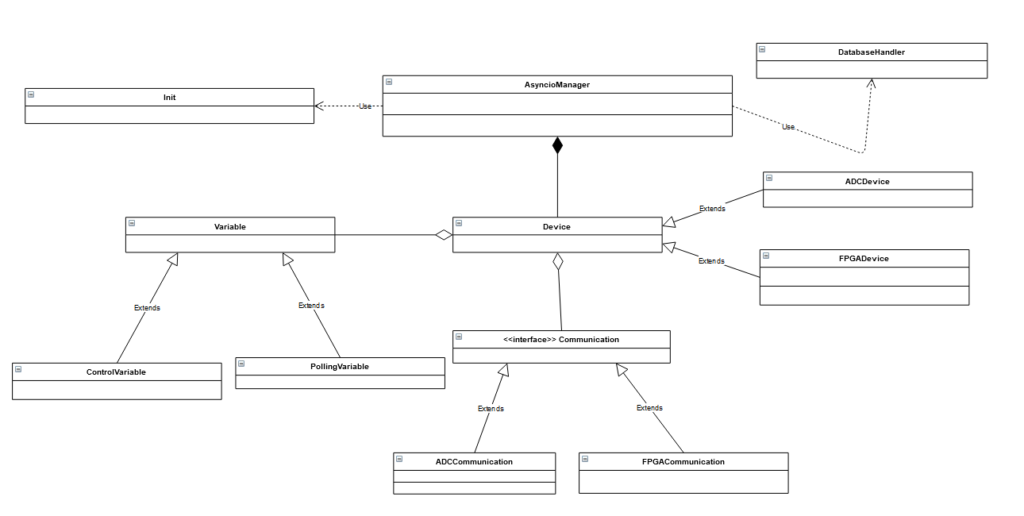

To provide more effective process management within the software design and the reception and transmission of controller data, curio a co-routine based library was implemented within our software base. This allows our software to handle every process in an asynchronous format which allows the management of both asynchronous requests such as communication to the generator in real time while allowing synchronous processes to run via a queuing system.

Furthermore, our design provides an effective platform for controller testing which can be easily re-built and replicated with commercially available hardware.

WHAT MAKES OUR DESIGN SOLUTION EFFECTIVE

Our design solution offers a simplistic yet extensible design which allows users of the device to replace the hardware components within set design limitations. This allows users to upgrade/side-grade existing devices while being able to use the same software design on the new platform with ease. Furthermore, our software is also designed with extensibility in mind to allow users to manipulate the sampled number/values.

HOW WE VALIDATED OUR DESIGN SOLUTION

To ensure our design was airtight, our group’s testing lead collaborated with our FPGA design lead and Python lead throughout the design process of each software module to ensure that they are functional and thoroughly tested with unit tests. Each piece of hardware was thoroughly researched and tested for functionality to ensure that they fit within the designed layout we had built.

Further validation was done by providing transparency to our academic advisors and sponsors during our design process to ensure they understand where our design stands and provide feedback if necessary.

FEASIBILITY OF OUR DESIGN SOLUTION

The design solution we have crafted during our first design review planned our intended timeline and scope of the capstone and ensured that each milestone would have leeway for possible scope creep, additions, or unintended circumstances. With that timeline set in stone, our design has been able to meet our requirements set for the minimum viable product along with various additions which our sponsor has agreed upon. The final product of our design will provide our sponsor with an extensible codebase and a remote user interface with in-depth documentation and functional pre-programmed hardware components.

The economic feasibility of this project has been taken into account as our total design cost has not exceeded our baseline comparison for designing the project. That baseline was the expected cost of purchasing a professional license of Matlab of $2711 cad (2150 usd). If replacements were necessary, each hardware asset which has been purchased by the group can be acquired via digikey.com and the software libraries used are all free to access.

Acknowledgements and Appreciation

Our team would like to extend our gratitude to our sponsor, Acceleware, for providing us with the opportunity to collaborate on an innovative oilsands project which may pave way for the future of Oil-sand extraction.

We want to thank everyone who has provided us assistance along our capstone Journey. Our two electrical academic advisors; Denis Onen and Vincent Grennerat have played an integral part in providing us vital feedback and assisting us through each challenges we faced. Furthermore, our sponsor contacts John Nielsen and Michal Okoniewski have been invaluable with their guidance throughout the project’s lifecycle.

Thank to all of our team members who have contributed to the project. Without them, this project literally could not have been accomplished in 8 months

Asadullah “Dips on the Big Cheese” Aftab for his excellent hardware management and assistance on the FPGA code component

John Carlo “1 hour coding, 23 hours compilation” Catapang for his continuous work on ensuring that the FPGA code component did not crumble into a million pieces

Taha “Depresso Expresso” Ghazaly for his guidance the FPGA, Hardware, and Software components and ensuring that everything was done with a reason

Alexander “Man without a plan” Le for his work in ensuring that all testing was done properly and the creation of the entire web-server user interface

Andy “The Boomer” Zheng for making sure the project was on track and handling all the paperwork

Our photo gallery

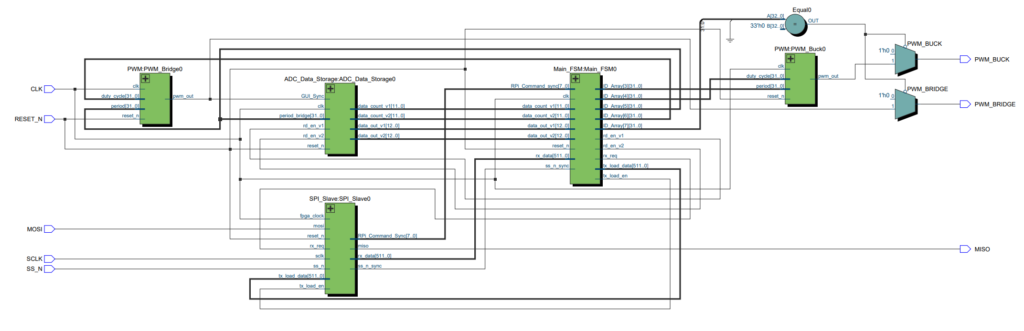

Full Logic Schematic of FPGA Component

Full Logic Schematic of Python Component

Graphics User Interface