Project Category: Electrical

About our project

This project is sponsored by I2Sense Lab at the University of Calgary. The project will be the schematic and layout designs and simulation of a complete chip using Cadence Virtuoso. If the simulations merit it, the chip will be tested and manufactured by staff at University. The software tools and manufacturing will be sponsored.

Meet our team members

Mike

BSc Electrical Engineering

Hardware Lead

Gaganvir

BSc Electrical Engineering

Hardware Lead

Austin

BSc Electrical Engineering

Verification Lead

Taku

BSc Electrical Engineering

INTEGRATION Lead

Randall

BSc Electrical Engineering

Project MANger,

Details about our design

HOW OUR DESIGN ADDRESSES PRACTICAL ISSUES

Typical cell phone cameras record up to 240 frames per second, industry-standard high-speed imagers like phantom cameras can record a million frames per second. But with eight pixels tall when it is operating at high speed, which means standard 12 font will be 16 pixels tall. That limits the use of these cameras at very high speed. Our design uses communication theory, which is able to increase the data rate at high-speed operations.

WHAT MAKES OUR DESIGN INNOVATIVE

Image sensor using communication theory is an emerging field in CMOS image sensor design. Our design will be exploring the potential, as well as limits of using it to build an image sensor chip, other method, such as wide dynamic range technology (WDRT) have equal potentials to be explored in the future.

HOW WE VALIDATED OUR DESIGN SOLUTION

Our project strictly followed design process of integrated circuits project, we built testbenches for each section, and present detailed technical specifications, after integration, we present waveforms and technical specifications for the product, if it attracts interests from industry, testing by FPGA will be conducted before it enters production.

FEASIBILITY OF OUR DESIGN SOLUTION

Due to COVID, our access to equipment is limited, all the tests for this project are performed on Cadence Design Software, we are only able to present technical specifications of schematic-level and layout-level designs. More serious testing must be conducted before it enters the fabrication phase, unfortunately, we could not perform that in the online version of the capstone project this year, which will be handled by staff and researchers from at U of C.

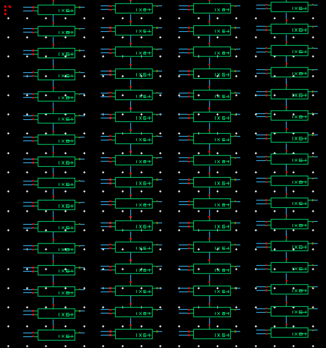

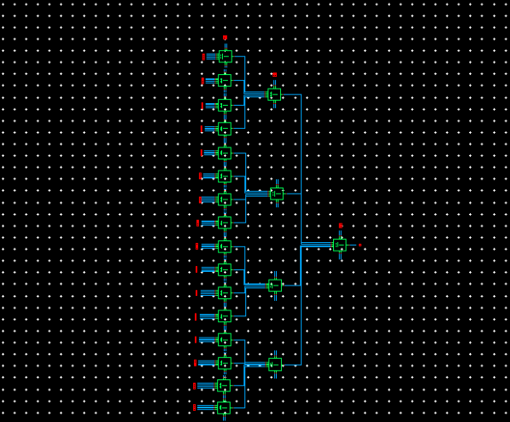

SCHEMATIC-LEVEL DESIGN

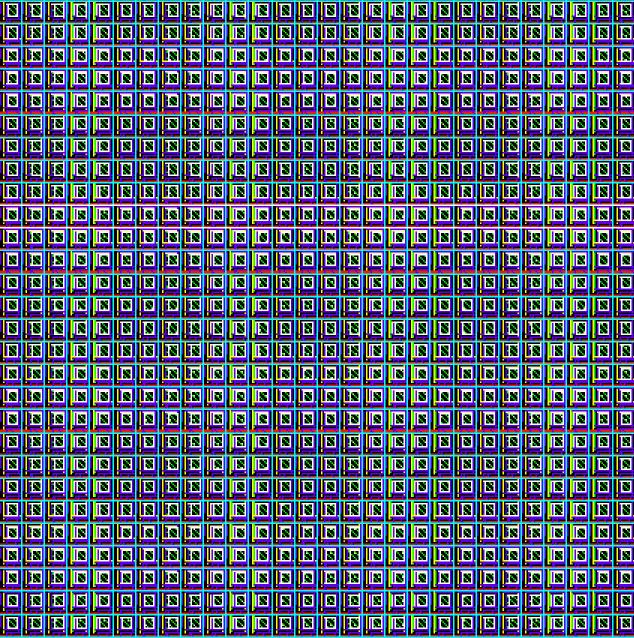

LAYOUT-LEVEL DESIGN

Partners and mentors

The team would like to express our sincere gratitude to all those who helped make our project a success. Professor at the University of Calgary, Dr. Yadid-Pecht, for informative lectures, expertise, and guidance on a capstone project. Associate director at I2Sense Lab, Mr. Devin Atkin, for enthusiastic demonstration and continued help throughout this academic year. ENEL 500 teaching assistant, Ms. Zahra Kabirkhoo, for giving the team continuous feedback and direction throughout the course deliverables and helping us consider all angles through challenging questions and insights.

Our photo gallery

People